LPL.RAM 48KB DYN. CAAC05

### Inhaltsverzeichnis

| Vergleich von dynamischen und statischen RAMs                                                     | 3  |

|---------------------------------------------------------------------------------------------------|----|

| Der dynamische RAM-Baustein 4116                                                                  | 4  |

| Kurzbeschreibung des dynamischen RAM-Controllers 8202                                             | 5  |

| Allgemeiner Überblick über die 48 kB-RAM-Baugruppe<br>CAAC 05 und die 32 kB-RAM-Baugruppe CAAC 06 | 8  |

| Die Schnittstelle zum alphatronic-Systembus                                                       | 8  |

| Die Adreßleitungen                                                                                | 8  |

| Die Datenleitungen                                                                                | 9  |

| Die Steuer- und Signalleitungen                                                                   | 10 |

| Die Refreshrequest-Ansteuerung                                                                    | 10 |

| Der asynchrone Refresh                                                                            | 10 |

| Der synchrone Refresh                                                                             | 11 |

| Funktionsbeschreibung der Refresh-Synchronisations-<br>logik                                      | 12 |

| Beispiel eines Timing-Diagramms für den dynamischen<br>Speicher                                   | 13 |

| Der Taktoszillator                                                                                | 17 |

| Die Erzeugung des RDY-Signals                                                                     | 18 |

| Die Brückenbelegungsliste                                                                         | 19 |

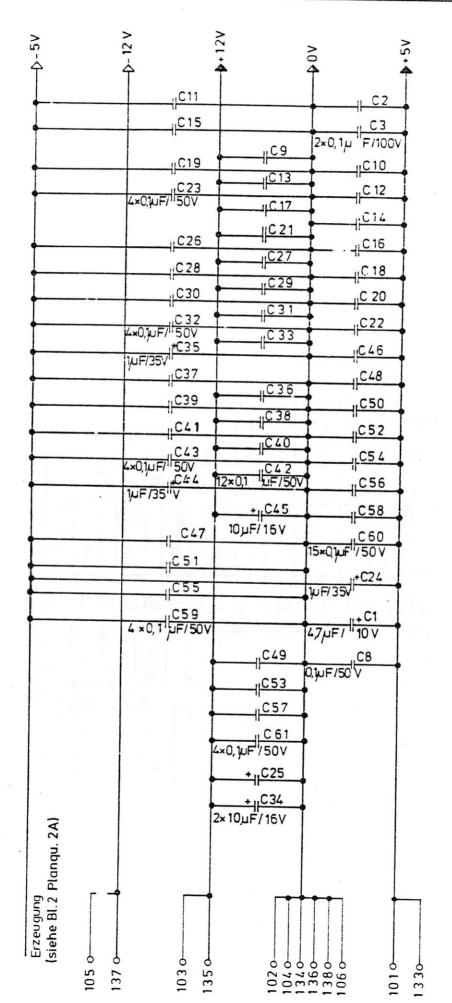

| Die Erzeugung der -5 Volt Betriebsspannung                                                        | 20 |

| Die Probleme der Stromversorgung                                                                  | 20 |

| Die Stromaufnahme der 48 kByte-RAM-Baugruppe CAAC 05                         | 22 |

|------------------------------------------------------------------------------|----|

| Die Stromaufnahme der 32 kByte-RAM-Baugruppe CAAC 06                         | 22 |

| Die Adreßbereiche und Bitzuordnung auf den Baugruppen<br>CAAC 05 und CAAC 06 | 23 |

| Steckerbelegungsliste                                                        | 24 |

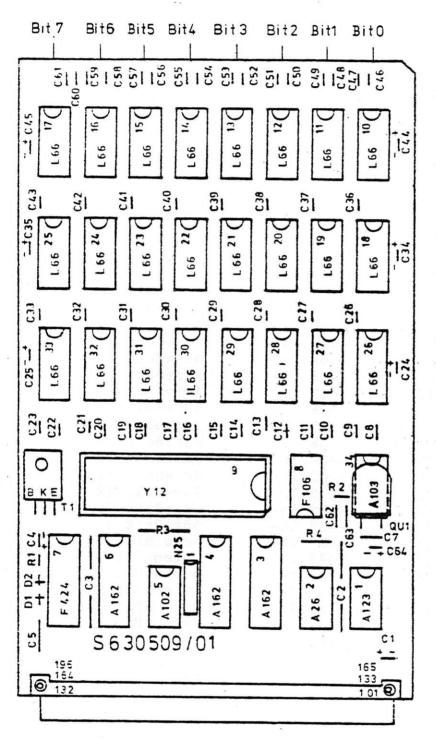

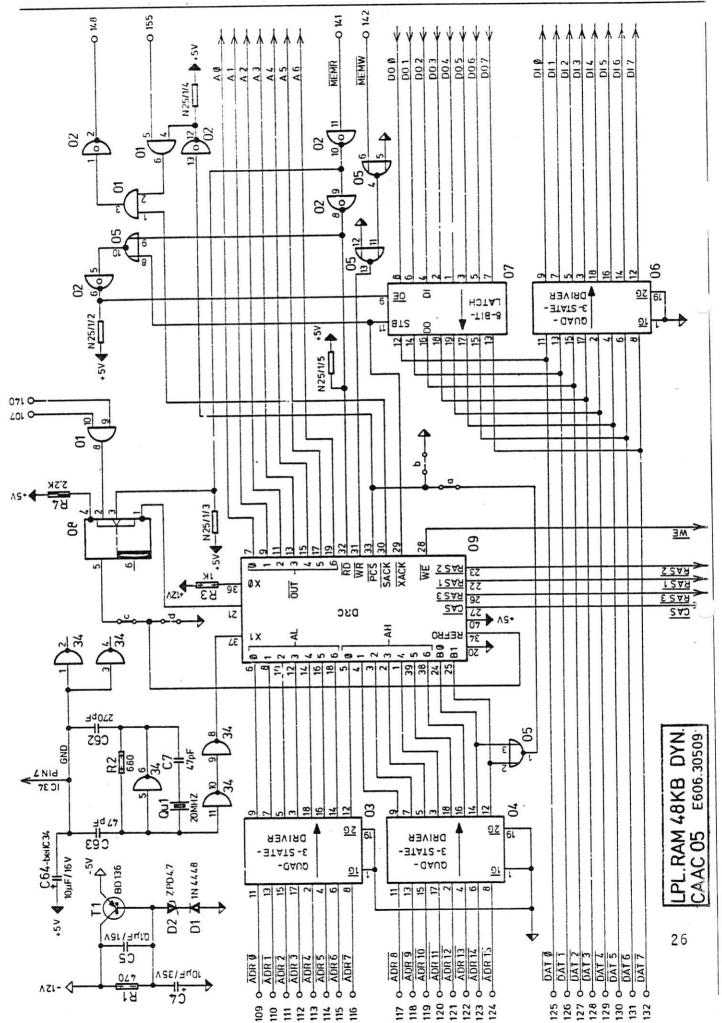

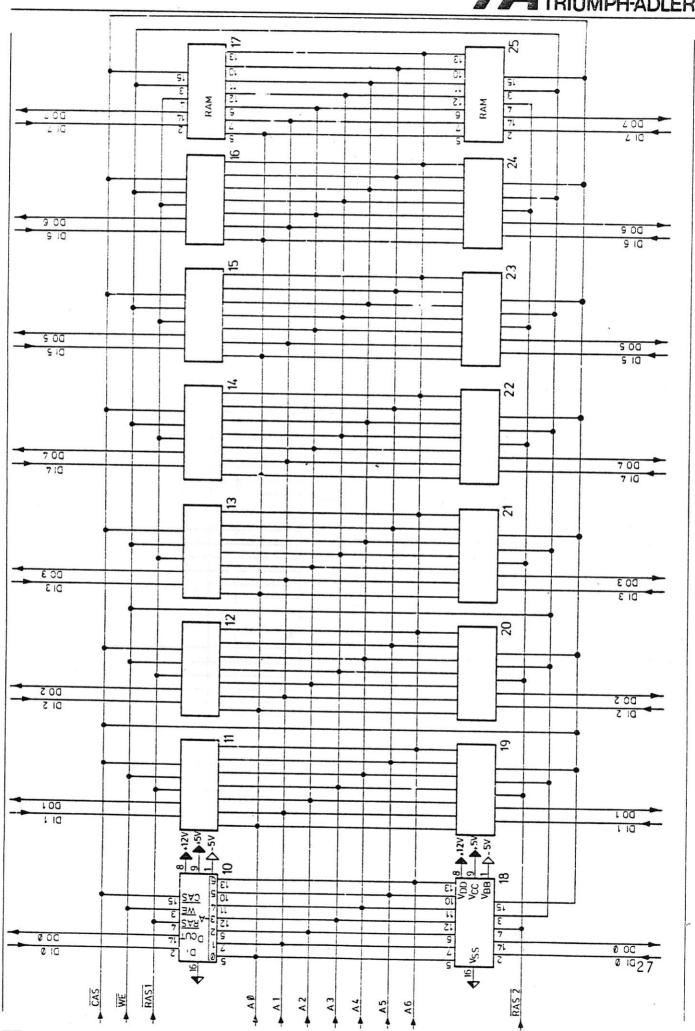

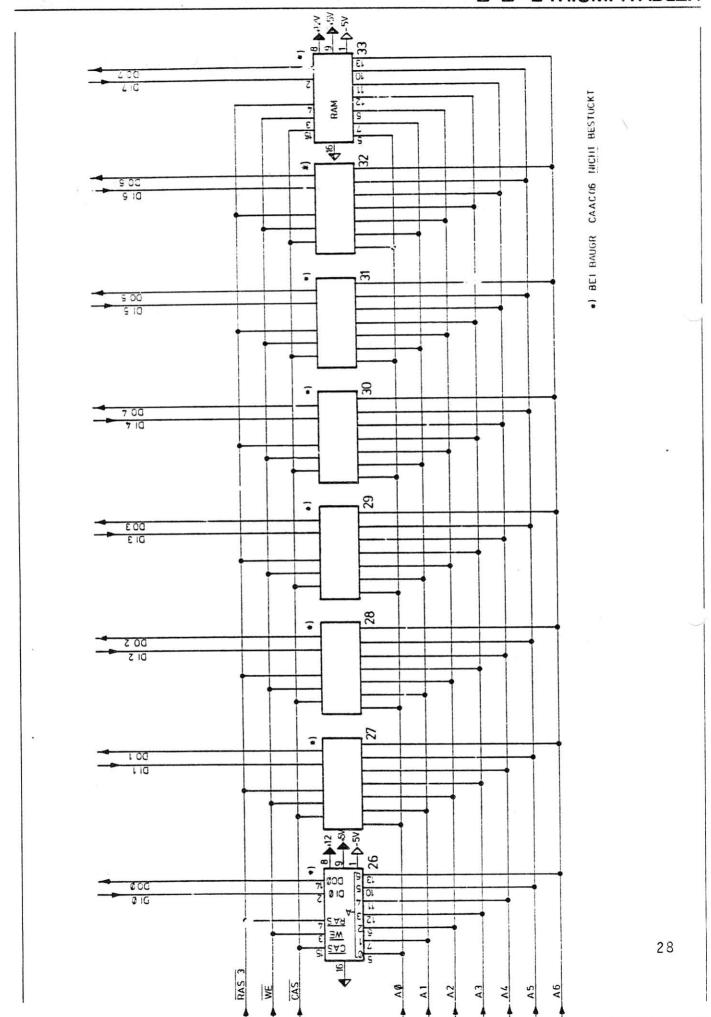

| Schaltbild                                                                   | 26 |

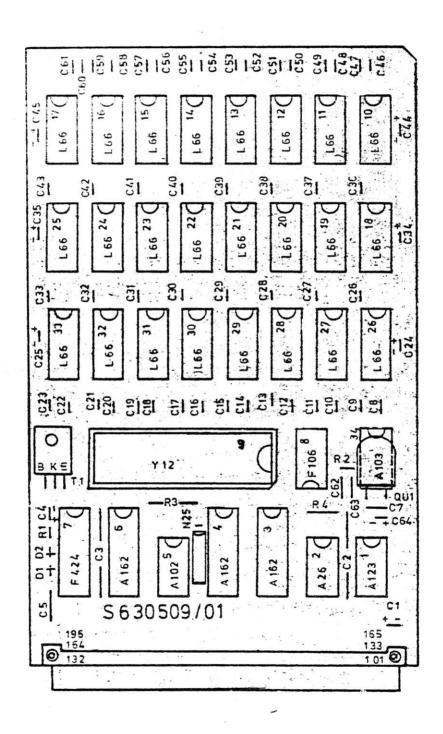

| Bestückungsplan                                                              | 30 |

| Blockschaltbild der 48kB dyn. RAM-Baugruppe                                  | 31 |

| Literaturverzeichnis                                                         | 32 |

Vergleich von dynamischen und statischen RAMs

Der prinzipielle Unterschied zwischen dynamischen und statischen RAMs liegt im Aufbau und der Organisation. So erfolgt bei statischen RAMs die Adressierung der jeweiligen RAM-Zelle über die Adreßeingänge direkt. Für einen statischen RAM-Baustein mit einer Kapazität von 16384 x 1 Bit sind 14 Adreßleitungen erforderlich. Dynamische RAMs hingegen benötigen nur 7 Adreßleitungen, da die Adresse gemultiplext anliegen.

RAM-Bausteinen wird die Information in Form dynamischen Kondensatorladungen jeweiligen von in den gespeichert. Durch Leckströme geht die Ladung in Damit hierdurch nicht auch Speicherkondensatoren verloren. die gespeicherte Information verloren geht, muß der Ladungsverlust der dynamischen Speicherzellen spätestens alle 2 msec regeneriert werden. Das Regenerieren der Speicherzellenladungen bezeichnet man als Refresh Auffrischen.

Statische RAM-Speicherzellen arbeiten wie Flipflops, in denen die Informationen solange gespeichert bleiben, bis die Information in die Speicherzelle neu eingeschrieben wird.

Dadurch, daß die statische Speicherzelle aus Flipflop-Schaltungen aufgebaut ist, benötigen statische RAM-Bausteine relativ viel Platz. Auch die Leistungsaufnahme ist im Verhältnis zu dynamischen RAM-Bausteinen viel größer.

Besonders bei großen Speichersystemen macht sich die Verminderung der Leistungsaufnahme bei Verwendung von dynamischen RAMs bemerkbar. Eine verminderte Leistungsaufnahme verursacht auch eine geringere Verlustleistung und dadurch bedingt auch eine geringere Wärmeentwicklung im System.

Die dynamische 48kB RAM Baugruppe CAACO5 hat eine Leistungsaufnahme von etwa 2,5 Watt. Um die gleiche Speicherkapazität bei Verwendung von statischen RAMs (2114) zu erhalten wäre eine Leistungsaufnahme von etwa 37 Watt erforderlich.

Der dynamische RAM-Baustein 4116

Dynamische Speicherbausteine sind in einer Matrixstruktur aufgebaut. Der in der 48 kByte-RAM-Baugruppe CAAC 05 und in der 32 kByte-RAM-Baugruppe CAAC 06 verwendete dynamische RAM-Baustein 4116 ist in einer Matrix von 128 Reihen (Rows) und 128 Spalten (Columns) organisiert.

Baustein verfügt über nur 7 Adreßeingänge (AO bis A6). Mit Adreßeingängen läßt sich der gesamte 4116 RAMs von 16384 X l Bit adressieren. diesen Adreßbereich des Hierzu werden die Adressen gemultiplext an die Adreßeingänge gelegt. Die Ausgabe der gemultiplexten Adressen übernimmt der RAM-Controller. Die ersten sieben Adreßbits geben die Reihenadresse (ROW-Adress) Reihenadresse wird an. Die zusammen -RAS--Signal mit dem (Row-Adress-Strobe) RAM-Bausteinen übergeben. Hiernach folgt die Spaltenadresse, zusammen mit dem -CAS--Signal (Column-Adress-Strobe) ausgesendet wird. Auf diese Weise lassen sich 128 X 128 16384 Speicherzellen adressieren. Durch gemultiplexten Adreßleitungen ist die Möglichkeit gegeben der geringen Bauteilgröße und der geringen Anzahl von 16 Pins dieses große Speichervolumen zu adressieren. Außer den sieben Adreßanschlüssen AO bis A6 besitzt der in dieser Baugruppe eingesetzte 4116 RAM-Baustein noch je einen für das -CAS- und -RAS--Signal. Hierzu kommen noch Anschluß weitere vier Anschlüsse für die drei Versorgungsspannungen und die GND-Leitungen.

Zur Verbindung mit dem Datenbus verfügt der Baustein über je einen Dateneingang und Datenausgang Anschlußpin (DIN und DOUT).

Die Auswahl, ob in den RAM-Baustein geschrieben oder ob aus ihm gelesen wird, erfolgt über den -WE--Anschluß.

Nebenstehendes Bild zeigt die Pinbelegung des RAMs 4116.

| -5 V<br>DIN<br>-WE-<br>-RAS-<br>AO | 1<br>2<br>3<br>4<br>5 | 16 -<br>15 -<br>14 -<br>13 -<br>12 - | GND<br>-CAS-<br>DOUT<br>A6<br>A3 |

|------------------------------------|-----------------------|--------------------------------------|----------------------------------|

| A 2                                | 6                     | īī ļ                                 | A4                               |

| Al                                 | 7                     | 10 +                                 | A 5                              |

| +12 V                              | 8                     | 9 +                                  | +5 V                             |

|                                    |                       |                                      |                                  |

Kurzbeschreibung des dynamischen RAM-Controllers 8202

Der dynamische RAM-Controller 8202 liefert alle, für den Betrieb des 16k X 1 Bit RAMs 4116 erforderlichen Signale.

Der Controller beinhaltet eine Vorrangschaltung, die den angeforderten Zyklus (Schreib-, Lese- oder Refresh-Zyklus) mit dem momentan laufenden Zyklus in Einklang bringt. Ein Refresh-Zyklus wird nur sofort ausgeführt, wenn momentan kein Schreib- oder Lesezyklus ausgeführt wird. Anderenfalls wird, sobald der vorausgegangene Zyklus beendet ist, der Refresh-Zyklus ausgeführt. Der 8202-Controller besitzt eine Logik, die dafür sorgt, daß spätestens alle 2 msec jede RAM-Zelle aufgefrischt wird. Diese Logik überwacht den REFRQ-Anschluß und generiert, wenn kein externer Refresh-Request vorliegt (High-Pegel am REFRQ-Eingang), die Refresh-Anforderung intern. Ein externer Refresh-Request setzt die interne Refresh-Logik zurück.

Das folgende Bild zeigt die Pin-Belegung des 8202.

|                                                                   | 2 |                                           |                                                    |                                                                                           |

|-------------------------------------------------------------------|---|-------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|

| AH4<br>AH3<br>AH2<br>AH1<br>AH0<br>AL0<br>-OUT0-<br>AL1<br>-OUT1- |   | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32 | - Vcc<br>- AH5<br>- AH6<br>- X1/CLK<br>- X0/OP2<br>- TNK<br>- REFRQ/ALE<br>PCS-<br>RD-/S1 |

| AL2                                                               |   | 10<br>11                                  | 31<br>30                                           | WR-<br>SACK-                                                                              |

| AL3<br>-OUT3-                                                     | - | 12                                        | 29<br>28                                           | XACK-<br>WE-                                                                              |

| AL4<br>-OUT4-                                                     | - | 14<br>15                                  | 27<br>26                                           | CAS-<br>RAS3-                                                                             |

| AL5<br>-OUT5-<br>AL6                                              |   | 16<br>17<br>18                            | 25<br>24<br>23                                     | - B1/OP1<br>- B0<br>RAS2-                                                                 |

| -OUT6-<br>Vss                                                     |   | 19<br>20                                  | 22<br>21                                           | RAS1-<br>- RASO-                                                                          |

In der folgenden Tabelle werden die Anschlüsse des RAM-Controllers 8202 so beschrieben, wie diese in der Schaltung der 48 kByte oder 32 kByte RAM-Baugruppe eingesetzt werden.

| Signal                                        | Pin                                  | Erklärung                                                                                                                                                                                              |

|-----------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc                                           | 40                                   | +5 Volt +/- 10%                                                                                                                                                                                        |

| Vss                                           | 20                                   | Masse (O Volt)                                                                                                                                                                                         |

| ALO<br>AL1<br>AL2<br>AL3<br>AL4<br>AL5<br>AL6 | 6<br>8<br>10<br>12<br>14<br>16<br>18 | Adreßeingänge für die niederen sieben<br>Adreßsignale. Aus diesen Adressen werden<br>die Reihenadressen für die Speicher-<br>zellen erzeugt.<br>Es sind 128 Reihen adressierbar.                       |

| AHO<br>AH1<br>AH2<br>AH3<br>AH4<br>AH5<br>AH6 | 5<br>4<br>3<br>2<br>1<br>39<br>38    | Adreßeingänge für die sieben oberen Adreßleitungen A7 - Al3. Aus diesen Adressen wird die Spaltenadresse für die gemultiplexte Speicherzellenadresse gebildet. Es sind somit 128 Spalten adressierbar. |

| B0<br>B1                                      | 24<br>25                             | Über die BO und Bl-Eingänge des RAM-Con-<br>trolers lassen sich die verschiedenen<br>RAM-Banks adressieren. (4 RAM-Banks)                                                                              |

| -RD-                                          | 32                                   | Low-Pegel an diesem Eingang zeigt einen<br>Lesezyklus an.                                                                                                                                              |

| -WR-                                          | 31                                   | Low-Pegel an diesem Eingang zeigt einen<br>Schreibzyklus an.                                                                                                                                           |

| -PCS-                                         | 33                                   | Low-Pegel an diesem Eingang gibt die RD-<br>und WR-Eingänge frei.<br>(protected chip select)                                                                                                           |

| Signal                                                             | Pin                            | Erklärung                                                                                                                                                                                                                         |

|--------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFRQ                                                              | 34                             | High-Pegel an diesem Eingang fordert<br>einen Refresh-Zyklus an. Bei Low-Pegel<br>wird der Refresh im Bedarfsfall durch<br>den im Baustein implementierten Timer<br>angefordert.                                                  |

| ΧO                                                                 | 36                             | Bei externer Takterzeugung muß dieser<br>Eingang über einen 12 kOhm Widerstand<br>mit +12 Volt Potential verbunden werden.                                                                                                        |

| X1/CLK                                                             | 37                             | Eingang für den externen Takt.                                                                                                                                                                                                    |

| -0UT0-<br>-0UT1-<br>-0UT2-<br>-0UT3-<br>-0UT4-<br>-0UT5-<br>-0UT6- | 7<br>9<br>11<br>13<br>15<br>17 | Ausgänge für die vom Multiplexer des RAM-Controllers erzeugte Speicherzellen-adresse. Es sind 128 X 128 = 16384 Speicherzellen über die sieben Adreßleitungen adressierbar.                                                       |

| -WE -                                                              | 28                             | Dieser Ausgang signalisiert den RAMs, ob<br>ein Schreib- oder Lesebefehl ausgeführt<br>werden soll.                                                                                                                               |

| -CAS-                                                              | 27                             | Strobesignal für die Übergabe der Spal-<br>tenadresse (column adress strobe).                                                                                                                                                     |

| -RASO-<br>-RAS1-<br>-RAS2-<br>-RAS3-                               | 21<br>22<br>23<br>26           | Strobesignal für die Übergabe der Reihen-<br>adresse (row adress strobe).<br>Bei einem Schreib-Lesezugriff auf den<br>Speicher ist nur ein Signal aktiv. Bei<br>einem Refresh-Zyklus sind alle RAS-<br>Signale aktiv. (Low-Pegel) |

| -XACK-                                                             | 29                             | Transfer Acknoledge. Low-Pegel an diesem Ausgang zeigt an, daß bei einem Lese-zyklus gültige Daten an den Dout-Aus-gängen der RAMs anstehen. Dieser Ausgang signalisiert auch gültige Daten bei einem Schreibzyklus.              |

| -SACK-                                                             | 30                             | System Acknolledge. Dieser Ausgang zeigt<br>den Beginn eines Speicherzugriffes an.                                                                                                                                                |

Allgemeiner Überblick über die 48 kB-RAM-Baugruppe CAAC 05 und die 32 kB-RAM-Baugruppe CAAC 06.

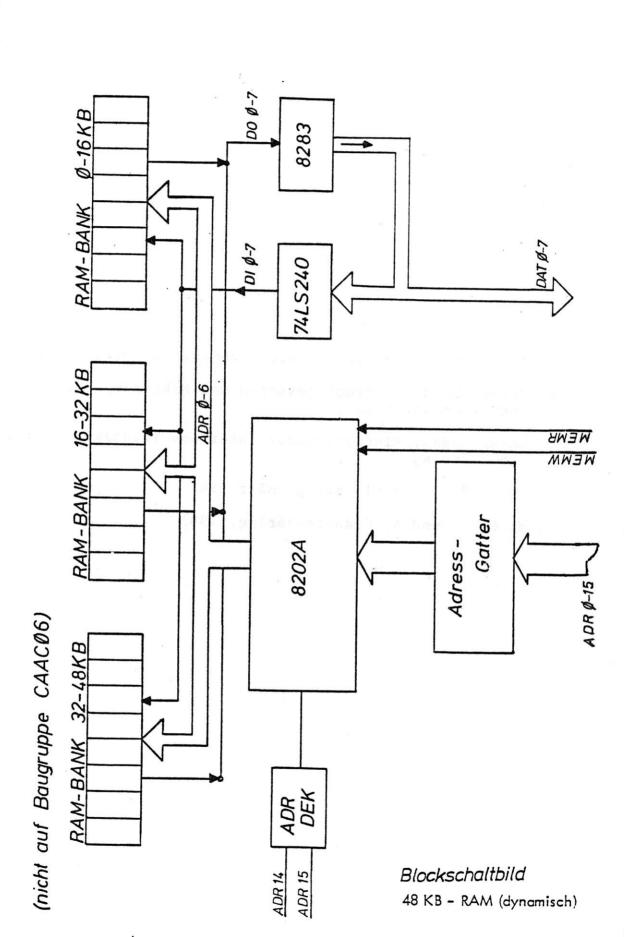

Wie das Blockschaltbild auf Seite 32 zeigt, besteht die CAAC 05 Baugruppe aus einem RAM-Controller für dynamische RAM-Bausteine, drei (zwei bei CAAC 06) RAM-Banks zu je 16 kByte, sowie einer Logik zur Adreßbereichserkennung und zur Steuerung des Datentreibers.

Die Baugruppe CAAC 06 entspricht der Baugruppe CAAC 05 mit der Einschränkung, daß die 16 kB-RAM-Bank mit dem Adreßbereich von hexadezimal COOO bis FFFF (RAM-Bank 32 bis 48 kB im Blockschaltbild) nicht bestückt ist.

Der RAM-Controller wandelt die 16 Bit breite Adresse, die auf dem alphaTronic-Systembus ansteht, in eine gemultiplexte Adresse um. Zusammen mit der gemultiplexten Adresse werden den RAM-Bausteinen auch die Übernahmesignale (CAS und RAS) gesendet.

Die Unterteilung des 64 kB Adreßbereiches in vier jeweils 16 kB große Bereiche erfolgt durch die RAS-Signale. Diese RAS-Signale werden durch die Adreßbits Al4 und Al5 des Systembusses aktiviert.

Der RAM-Controller überwacht den Refresh der RAM-Zellen. Die Refresh-Anforderungen können sowohl intern als auch extern erzeugt werden.

Die Schnittstelle zum alphaTronic-Systembus

Die Adreßleitungen

Die Adreßleitungen (-AO- bis -Al5-) des alphaTronic-Systembusses werden auf der RAM-Baugruppe durch zwei IC-Bausteine vom Typ 74LS240 (IC 03 und IC 04) entkoppelt. Diese Bustreiberbausteine arbeiten invertierend und besitzen Schmitt-Trigger-Eingänge, wodurch die Flankensteilheit Adreßsignale wieder erhöht wird. Gatter mit Schmitt-Trigger-Eingängen unterdrücken die Weiterleitung von Störsignalen und tragen damit zur Erhöhung Störsicherheit bei.

Die Ausgänge der Bustreiberbausteine (IC 03 und IC 04) sind ständig freigegeben, da die beiden Freigabeeingänge -IG- und -2G- (Pin 1 und 19) auf Low-Pegel (Masse) liegen. Die Adressen liegen somit ständig am RAM-Controller an. Die eingesetzten Bustreiberbausteine (IC 03 und IC 04, 74LS240) liefern invertierte Ausgangssignale. Dadurch, daß der alphaTronic-Systembus Low-aktiv ist, sind die Adreßsignale auf der RAM-Baugruppe High-aktiv.

#### Die Datenleitungen

Die Datenleitungen des alphaTronic-Systembusses werden von der RAM-Baugruppe durch ein Latch vom Typ 8283 (IC 07) und durch einen Bustreiberbaustein vom Typ 74LS240 (IC 06) entkoppelt. Sowohl das Latch (8283), als auch der Bustreiber (74LS240) besitzen invertierende Ausgänge. Dieses ist erforderlich, da der alphaTronic-Bus Low-aktiv ist.

Der Bustreiber (IC 06) ist so geschaltet, daß die Datenflußrichtung vom Systembus zur RAM-Baugruppe ist. Die Ausgänge dieses Bustreiber ICs sind ständig freigegeben, da die Freigabeeingänge -IG- und -2G- (Pin 1 und 19) auf Low-Pegel liegen. Jeder Ausgang des Bustreibers ist mit je einem Dateneingang in jeder RAM-Bank verbunden.

Die Datenausgabe von der RAM-Baugruppe zum alphaTronic-Systembus wird über das 8-Bit Latch (IC 07, 8283) gesteuert. Die Ausgänge dieses Bausteines werden freigegeben, wenn Daten aus dem RAM gelesen werden, und diese auch gültig anliegen.

Am -OE--Eingang dieses Latches (IC 07, Pin 9) liegt Low-Pegel an, wenn das -MEMR- und -XACK--Signal Low-Pegel hat. Die Ausgänge des Latches werden freigegeben, wenn ein Lesezyklus auf den Adreßbereich der RAM-Karte durchgeführt wird und der RAM-Controller mit Low-Pegel am -XACK--Ausgang anzeigt, daß die Daten an den DOUT-Ausgängen der RAMs gültig sind.

Über den STB-Eingang des Latches (IC 07, Pin 11) werden die gültigen Daten, welche aus den RAMs gelesen werden mit der 1/0-Flanke des -XACK--Signals im Latch abgespeichert. Der synchrone Refresh

Für die Betriebsart "synchroner Refresh muß Brücke c geschlossen und d offen sein.

Der Vorteil des synchronen Refresh liegt darin, daß die RAM-Zellen dann aufgefrischt werden, wenn seitens der CPU kein Speicherzugriff erfolgt. In der Betriebsart "Synchroner für die CPU keine Zugriffsverzögerung Refresh. erfolgt dadurch, daß erst ein augenblicklich ablaufender Refresh-Zyklus abgewartet werden muß. Der Prozessor bemerkt Auffrischvorgang nicht; daher bezeichnet man diesen Refresh auch als \*transperenten Refresh ...

Eine weitere Bezeichnung für diesen synchronen Refresh ist auch Hidden Refresh.

Damit jeder Refresh als Hidden Refresh ausgeführt wird, ist spätestens alle 15,6 µsec eine externe Refresh-Anforderung erforderlich. Wird diese Bedingung nicht erfüllt, so generiert der RAM-Controller seine Refresh-Anforderungen selbst. Diese Refresh-Zyklen werden dann wie beim asynchronen Refresh ausgeführt.

Die 8085 A CPU der alphaTronic besitzt zwei Statusleitungen SO und S1. Haben beide Leitungen H-Pegel, so handelt es sich um einen "Opcode-Fetch Zyklus. Als "Opcode-Fetch bezeichnet man den Zyklus, in dem die CPU einen Operationscode aus dem Speicher holt und diesen dekodiert. Da in diesem Zyklus der Befehl dekodiert wird, ist der Zyklus bei den meisten Prozessoren um einen Taktzyklus länger. Ein Opcode-Fetch-Zyklus ist somit sehr gut geeignet, um Refresh-Zyklen für den Prozessor unsichtbar durchzuführen.

Funktionsbeschreibung der Refresh-Synchronisationslogik

Die beiden Prozessor-Statussignale SO und Sl werden über ein UND-Gatter (IC Ol) miteinander verknüpft. Der Ausgang des UND-Gatters ist mit dem D-Eingang des Flipflop ICs (IC O8) verbunden. Am D-Eingang des Flipflops liegt immer dann High-Pegel an, wenn ein Opcode-Fetch von der 8085-CPU ausgeführt wird.

Mit der 0/l-Flanke des MEMR-Signals wird die Information, die am D-Eingang des Flipflops (IC 08, Pin 2) anliegt übernommen.

Q-Ausgang (Pin 5) erhält immer dann H-Pegel, wenn ein 0000 bis FFFF Opcode-Fetch im gesamten Adreßbereich von Der Q-Ausgang ist mit dem hexadezimal ausgeführt wird. REFRQ-Eingang des RAM-Controllers (IC 09, Pin 34) verbunden. REFRQ-Eingang signalisiert diesem High-Pegel an daß eine Refresh-Anforderung vorliegt. Während bei einem Refresh-Zyklus alle RAS-Signale Low-Pegel annehmen den angeschlossenen RAMs die gleiche Reihenadresse In allen angeschlossenen RAMs werden hierdurch 128 Bit einer Reihe aufgefrischt. Die Reihenadresse wird bei den nächsten Refresh-Zyklen solange erhöht bis alle Reihen aufgefrischt wurden. Danach wird der nächste Refresh mit der Reihenadresse O gestartet.

Das RASO-Signal (IC 09, Pin 21) ist mit dem Clear-Eingang des Flipflops (IC 08, Pin 1) verbunden. Low-Pegel, das heißt ein Refresh-Zyklus ist in der Ausführung, setzt die am REFRQ-Eingang (IC 09, Pin 34) anliegende Refresh-Anforderung zurück. Die Rücknahme der Refresh-Anforderung (High-Pegel am REFRQ-Eingang, IC 09,Pin 34) ist erforderlich, da sonst ein weiterer Refresh-Zyklus eingeschoben wird.

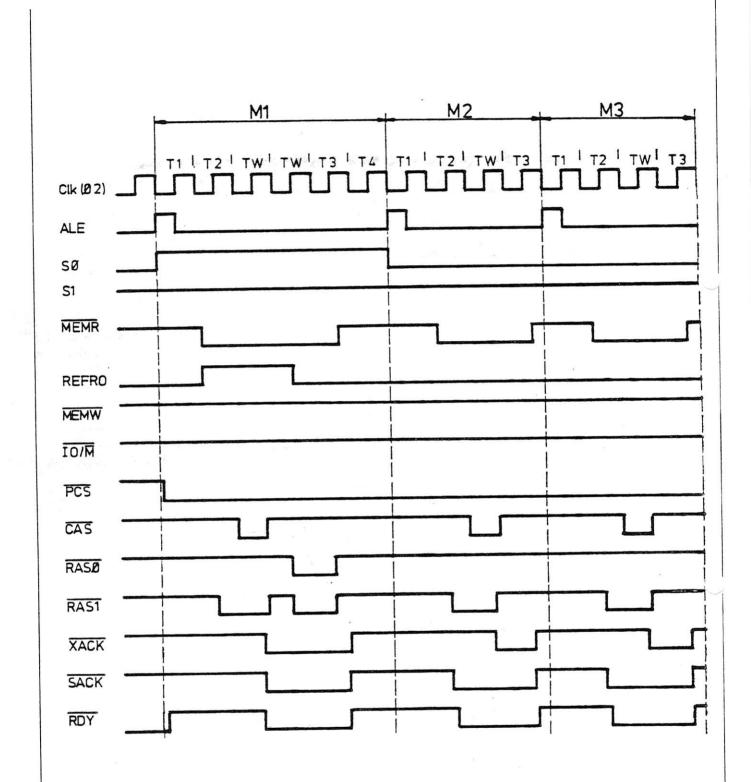

Beispiel eines Timing-Diagramms für den dynamischen Speicher

Das Timing-Diagramm auf Seite 16 zeigt den zeitlichen Verlauf der Steuersignale bei der Abarbeitung des Befehles JMP. Hierzu wird das folgende Beispielprogramm mit dem MOS-Befehl S (Substitute) ab der Speicheradresse 4010 eingegeben und mit dem Befehl G (Go) gestartet. Das Programm führt einen Sprung auf sich selbst aus.

| Beispielprogramm: | Hex.Adresse          | Hex.Code       | Mnemonic |

|-------------------|----------------------|----------------|----------|

|                   | 4010<br>4011<br>4012 | C3<br>10<br>40 | JMP 4010 |

Der JMP-Befehl wird in drei Maschinen-Zyklen, die mit Ml, M2 und M3 bezeichnet sind, ausgeführt. Im Ml-Zyklus wird der OP-Code, im Beispiel der hexadezimale Code C3 (JMP- Befehlscode), aus dem Speicher gelesen. In den Zyklen M2 bis M3 wird der Operand, im Beispiel die Sprungadresse 4010, aus dem Speicher gelesen.

#### Allgemeines

Als Referenzsignal wird das Taktsignal der CPU (CLK-Signal) an erster Stelle aufgezeigt. (Taktfrequenz 3MHz, Periodendauer 333 nsec)

Den Beginn der einzelnen Maschinenzyklen erkennt man daran, daß das ALE-Signal High-Pegel annimmt.

Die Ready-Abfrage durch die CPU erfolgt mit der O/1-Flanke des Taktes von T2. Hat der READY-Eingang zu dieser Zeit Low-Pegel, so werden solange Wait-Zyklen (Tw) eingefügt, bis bei der nächsten O/1-Flanke des Taktes High-Pegel an diesem Eingang anliegt.

Die Signale -MEMW- und -IO/-M-- haben im Timing-Diagramm, bedingt durch die Wahl des Beispiels, High-Pegel.

Der M1-Zyklus

Der Ml-Zyklus beginnt mit der Aktivierung des ALE-Signals. Diesen Zyklus erkennt man daran, daß die Statussignale S0 und S1 der CPU und das Signal -IO/-M-- High-Pegel haben.

Das -MEMR--Signal wird nach der 1/0-Flanke des T2-Taktes aktiv (Low-Pegel). Es behält bis nach der 0/1-Flanke des T3-Taktes Low-Pegel. Mit der 0/1-Flanke des -MEMR--Signals übernimmt der Prozessor die Daten vom Bus. Bis dahin müssen die Daten stabil sein.

Mit der 1/0-Flanke des -MEMR--Signals übernimmt der Ausgang Q des Flipflops (IC 08, Pin 5) die Information vom D-Eingang (IC 08, Pin 2). An diesem D-Eingang liegen die UND-Verknüpften Statussignale SO und Sl an. Das REFRQ-Signal nimmt nach der 1/0-Flanke des -MEMR--Signals High-Pegel an, wenn beide Statussignale SO und Sl High-Pegel besitzen.

Das Demonstrationsprogramm greift nur auf die hexadezimalen Adressen von 4010 bis 4012 zu. Diese Adressen liegen in dem kB-Adreßblock von 4000 bis 7FFF. Der 8202-RAM-Controller 1) (RAM-Bank durch selektiert diesen Bereich der 1/0-Flanke des -RAS1--Signals wird -RAS1--Signal. Mit die der Controller über die -OUTl- bis Reihenadresse, -OUT6--Ausgänge ausgibt, von den Row Adress Buffer der der RAM-Bank 1 übernommen. Alle anderen -RAS--Signale haben zu dieser Zeit High-Pegel.

Nach der Ausgabe der Reihenadresse wird über die gleichen Ausgänge des RAM-Controllers die Spaltenadresse ausgegeben. Das Anliegen der Spaltenadresse wird durch Low-Pegel am -CAS--Signal signalisiert. Mit der 1/0-Flanke dieses Signals wird die Spaltenadresse in die Column Adress Buffer übernommen.

das -RAS1--Signal Low-Pegel 200 nsec, nachdem Maximal hat, liegen an den DOUT-Ausgängen der RAM-Bank l angenommen mit 200 nsec Zugriffszeit) gültige Daten an. Das (4116-RAMs der RAM-Controller Daten zeigt gültiger der 1/0-Flanke des am -XACK--Ausgang an. Mit Low-Pegel Latch (IC Daten im -XACK--Signals werden die abgespeichert.

Das -RDY--Signal, gemessen an ICO2 Pin 1, nimmt High-Pegel an, wenn das -PCS--Signals Low-Pegel liegt. Am RDY-Eingang der CPU liegt dann Low-Pegel an. Das -RDY--Signal hat solange High-Pegel, bis das -SACK--Signal Low-Pegel annimmt.

Eine kurze Zeit, nachdem das -RASI- und -CAS--Signal wieder High-Pegel angenommen haben, wird der Refresh-Zyklus durchgeführt. Hierzu nehmen alle -RAS--Leitungen Low Pegel an. Da die -RASO--Leitung mit dem Clear-Eingang des Flipflops (IC 08, Pin 1) verbunden ist, wird die Refresh-Anforderung durch Low-Pegel am -RASO--Signal zurückgenommen.

Der M2-Zyklus

Der M2-Zyklus des Beispieles besteht aus drei Taktzyklen und einem Wait-Zyklus Tw. In diesem Zyklus wird das niederwertige Bit der Sprungadresse eingelesen.

Der M2-Zyklus wird wieder durch High-Pegel auf der ALE-Leitung signalisiert.

Da ein Memory-Readm-Zyklus ausgeführt wird, hat das Statussignal SO Low-Pegel und Sl High-Pegel.

Nach der 1/0-Flanke des T2-Taktes nimmt das -MEMR--Signal bis nach der 0/1-Flanke von T3 Low-Pegel an.

In diesem Zyklus liegt keine Refresh-Anforderung vor.

Die Adressierung der RAM-Zelle erfogt wie beim M1-Zyklus beschrieben. Äquivalent zum M1-Zyklus verhalten sich auch die Signale -XACK-, -SACK- und -RDY-.

Der M3-Zyklus

Der M3-Zyklus des Beispieles besteht aus drei Taktzyklen und einem Wait-Zyklus. Im M3-Zyklus wird das höherwertige Byte der Sprungadresse eingelesen.

Die Signale verhalten sich wie beim M2-Zyklus.

Timing-Diagramm für den dynamischen Speicher

Der Taktoszillator

Verwendung des internen RAM-Controller Oszillators (IC 36 09, Pin 37) und führt bei Controllern Ausführungsstand 8202 8202A/S4354 zu Schwingungen auf und den -OUTO- bis -OUT6--Leitungen. Dieser Umstand ist auf Bausteinfehler des Controllers zurückzuführen. Durch einen seperate Erzeugung des für den RAM-Controller notwendigen Taktes treten keine Probleme auf.

Taktoszillatoren mit hohen Ausgangsfrequenzen erfordern eine "saubere "Umgebung. Das heißt, es dürfen keine Ausgänge dieses ICs unkontrolliert schalten. Aus diesem Grund sind die Eingänge der nicht benötigten Gatter von IC 34 auf Massepotential gelegt. Zur Stabilisierung der Versorgungsspannung an IC 34 wird der Kondensator C64 verwendet.

Die Gatter (IC 34, Pin 11 und 10 und Pin 9 und 8) dienen der Entkopplung des Oszillators.

Der Taktoszillator liefert eine Taktfrequenz von 20 MHz.

Die Erzeugung des RDY-Signals

Das RDY-Signal dient im alphaTronic Computersystem zur Generierung von Wait-Zyklen. Die 8085A CPU fragt bei der O/1-Flanke des T2-Zyklus in jeden Maschinen-Zyklus (M-Zyklus) den READY-Eingang ab. Liegt zu diesem Zeitpunkt Low-Pegel an, so werden solange Wait-Zyklen eingefügt, bis bei der nächsten O/1-Flanke des CPU Taktes wieder High-Pegel an diesem Eingang anliegt. Die CPU führt in dieser Zeit keine Befehle aus.

Durch das Timing bedingt ist es erforderlich, bei jedem Zugriff auf den dynamischen Speicher (Baugruppe CAAC 05 und CAAC 06) erforderlich einen Wait-Zyklus einzufügen.

Das RDY-Signal an Pin 148 der Steckerleiste nimmt für eine bestimmte Zeit Low-Pegel an, wenn ein Schreib- oder Lese-Zyklus auf den RAM-Adreßbereich von 4000 bis FFFF hexadezimal ausgeführt wird.

Das RDY-Signal wird gebildet aus der Verknüpfung der Signale -PCS-, -IO/-M-- (Pin 155 der Steckerleiste) und -Sack- nach der folgenden Boolschen Gleichung:

$$\overline{PCS}$$

.  $\overline{IO/M}$  .  $\overline{SACK}$  = RDY

Das RDY-Signal der RAM-Baugruppe hat an IC 02 Pin 2 immer dann Low-Pegel, wenn ein Zugriff auf diesen Speicher erfolgt und das -SACK--Signal High-Pegel besitzt.

Der alphaTronic-Systembus verfügt über nur eine RDY-Leitung. Da aber die Möglichkeit gegeben sein muß, daß auch andere Baugruppen Wait-Zyklen generieren können, müssen als Ausgangstreiber zu dieser Leitung Open-Collector-Gatter verwendet werden.

## Die Brückenbelegungsliste

| Brücke | geschl. | offen | Erklärung                                   |

|--------|---------|-------|---------------------------------------------|

| а      | Χ       |       | -PCS- wird Low, wenn                        |

| b      |         | Х     | Adresse zwischen 4000 und FFFF hexadezimal. |

| а      |         | Х     | -PCS- hat immer Low-                        |

| b      | Х       | -     | - Pegel                                     |

| С      | Х       |       | Betriebsart Hidden                          |

| d      |         | Х     | Refresh <sub>m</sub> "                      |

| С      |         | X     | Betriebsart                                 |

| d      | Х       |       | masynchroner Refresh                        |

Werkseitig sind die Brücken dieser Baugruppe so kaschiert, daß der Adreßbereich dieser Baugruppe von 4000 bis FFFF hexadezimal liegt und die Betriebsart "Hidden Refresh" gewählt ist.

Die Erzeugung der -5 Volt Betriebsspannung

Zum Betrieb der dynamischen RAM-Bausteine ist neben der +5 und +12 Volt Betriebsspannung auch eine -5 Volt Spannung erforderlich. Diese -5 Volt Spannung wird aus der -12 Volt Versorgungsspannung gewonnen.

Die -12 Volt Betriebsspannung wird über einen Vorwiderstand Ohm) der Spannungsstabilisierungsschaltung, 470 (1N4448) und D2 (ZPD 4,7) zugeführt. Der D1 gebildet aus legt den Arbeitspunkt für die Dioden fest. Vorwiderstand so ausgelegt, daß an der Basis des Diese Schaltung ist Tl (BD 136) eine Spannung im Bereich Längsregeltransistors anliegt. Für die geregelte 5.8 Volt 5.0 Ausgangsspannung am Emitter des Transistors Il ist ein Wert von -5 Volt +/- 10% zulässig.

Der Kondensator C4 dient zur Stabilisierung der Referenzspannung.

Die Probleme der Stromversorgung

Die Stromversorgung der RAMs ist sehr kritisch, da während der Adressierung und während Refresh-Zyklen sehr hohe Belastungen auf die Stromversorgung wirken. Besonders bei Refresh-Zyklen treten sehr hohe Stromspitzen auf, da hierbei jeweils eine Reihe (128 Speicherzellen) in allen RAMs auf der Speicherkarte gleichzeitig aufgefrischt wird.

Diese "Current Spikes", so bezeichnet man die Stromspitzen, verursachen Einbrüche der Versorgungsspannungen. Diese Spannungseinbrüche vermindern die Betriebssicherheit des Speichers erheblich. Die Spannungseinbrüche lassen sich dadurch vermeiden, daß nahe an den Spannungseingängen der ICs Kondensatoren mit einer Kapazität von etwa 0,1  $\mu F$ zwischen Spannung und Masse angeordnet werden.

Bei den kurzzeitig auftretenden Stromspitzen sorgt der Kondensator für einen Ladungsausgleich. In diesem Moment wird der Kondensator entladen. Aufgeladen wird dieser wieder, wenn normale Ströme fließen.

Im Bereich der RAMs sind auf der Baugruppe insgesammt 48 Kondensatoren mit einer Kapazität von 0.1 µF zwischen den Leiterbahnen für die verschiedenen Versorgungsspannungen und Masse angeordnet.

70 mA

max.

## Die Stromaufnahme der 48 kByte-RAM-Baugruppe CAAC 05

## Die Stromaufnahme der 32 kByte-RAM-Baugruppe CAAC 06

| + 5 V +/- 5%  | Stromaufnahme: | typ.<br>max. |          |  |

|---------------|----------------|--------------|----------|--|

| + 12 V +/- 5% | Stromaufnahme: | typ.<br>max. |          |  |

| - 12 V +/- 5% | Stromaufnahme: | typ.<br>max. | 40<br>50 |  |

BANK 1 Adresse 4000-7FFF

BANK 2 Adresse 8000-BFFF

BANK 3 Adresse COOO FEFF BANK 3 ist in der Baugruppe CAAC Ø6 nicht bestückt

Adreß - und Bitzuordnung auf den Baugruppen CAAC Ø 5 (48KB RAM) und CAAC Ø 6 (32 KB RAM)

# Steckerbelegungsliste:

| PIN                             | Bezeichnung                                  | Erklärung                |

|---------------------------------|----------------------------------------------|--------------------------|

| 101<br>102<br>103<br>104<br>105 | + 5 V<br>O V<br>+12 V<br>O V<br>-12 V<br>O V |                          |

| 106<br>107                      | SO                                           | Statussignal SO          |

| 108<br>109                      | -ADR O-                                      | Adreßbit O               |

| 110                             | -ADR 1-                                      | Adreßbit l               |

| 111                             | -ADR 2-                                      | Adreßbit 2               |

| 112                             | -ADR 3-                                      | Adreßbit 3               |

| 113                             | -ADR 4-                                      | Adreßbit 3<br>Adreßbit 4 |

| 114                             | -ADR 5-                                      | Adreßbit 5               |

| 115                             | -ADR 6-                                      | Adreßbit 6               |

| 116                             | -ADR 7-                                      | Adreßbit 7               |

| 117                             | -ADR 8-                                      | Adreßbit 8               |

| 118                             | -ADR 9-                                      | Adreßbit 9               |

| 119                             | -ADR 10-                                     | Adreßbit 10              |

| 120                             | -ADR 11-                                     | Adreßbit 11              |

| 121                             | -ADR 12-                                     | Adreßbit 12              |

| 122                             | -ADR 13-                                     | Adreßbit 13              |

| 123                             | -ADR 14-                                     | Adreßbit 14              |

| 124                             | -ADR 15-                                     | Adreßbit 15              |

| 125                             | -DAT O-                                      | Daten-Bit O              |

| 126                             | -DAT 1-                                      | Daten-Bit 1              |

| 127                             | -DAT 2-                                      | Daten-Bit 2              |

| 128                             | -DAT 3-                                      | Daten-Bit 3              |

| 129                             | -DAT 4-                                      | Daten-Bit 4              |

| 130                             | -DAT 5-                                      | Daten-Bit 5              |

| 131                             | -DAT 6-                                      | Daten-Bit 6              |

| 132                             | -DAT 7-                                      | Daten-Bit 7              |

# Steckerbelegungsliste

| PIN                                                                                     | Bezeichnung                                                              | Erläuterungen                                  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|

| 133<br>134<br>135<br>136<br>137<br>138<br>139<br>140<br>141<br>142<br>143<br>144<br>145 | + 5 V<br>0 V<br>+ 12 V<br>0 V<br>- 12 V<br>0 V<br>S1<br>-MEMR-<br>-MEMW- | Statussignal Sl<br>Memory-Read<br>Memory-Write |

| 147<br>148<br>149<br>150<br>151<br>152                                                  | RDY                                                                      | Ready-Signal                                   |

| 153<br>154<br>155<br>156<br>157<br>158<br>159<br>160<br>161<br>162<br>163<br>164        | -IO/-M                                                                   | I/O-Erkennung                                  |

#### Literaturverzeichnis

- 1. intel, Application Note AP 45, 1978

- 2. intel, Component Data Catalog 1981

- 3. Siemens, Mikrocomputer Bausteine, Band 2, Speicher

- 4. Texas Instruments, The MOS Memory Data Book, 1979

- 5. Siemens, Mikrocomputer Bausteine, Mikroprozessor System SAB 8085, Datenbuch 180/81

- 6. Ditmar Benda, Mikroprozessortechnik, VDE-Verlag, 1979

- 7. Werner Diehl, Mikroprozessoren und Mikrocomputer Vogel-Verlag, 1978

- 8. Zaks/ Lesea, Mikroprozessor Interface Techniken, 1981, Sybex-Verlag

- 9. Chip NR. 3, Vogel-Verlag, März 1981

- 10. mc Nr. 3 und 4, Franzis-Verlag, 1981

Die Steuer- und Signalleitungen

Die Steuer- und Signalleitungen, die zum Betrieb der RAM-Baugruppe erforderlich sind, werden durch Gatter vom Bus entkoppelt. Diese Gatter erfüllen zum Teil auch logische Aufgaben.

Die Refreshrequest-Ansteuerung

Bei der 48 kByte (32 kByte) dynamischen RAM-Baugruppe läßt sich der Refreshrequest für den RAM-Controller auf zwei verschiedenen Wegen erzeugen.

Der asynchrone Refresh

In der Betriebsart  $_{\mathbf{m}}$ asynchroner Refresh $_{\mathbf{m}}$  ist die Brücke C offen und die Brücke D geschlossen.

In dieser Betriebsart erzeugt der dynamische RAM-Controller seine Refresh-Anforderungen selbst. Spätestens alle 2 msec muß jede dynamische RAM-Zelle aufgefrischt werden. Bei jedem Refresh-Zyklus werden 128 Zellen einer Reihe der internen eines jeden angeschlossenen RAM-Bausteines aufgefrischt. Daraus, daß jede der 16384 RAM-Zellen eines Bausteines spätestens alle 2 msec aufgefrischt werden und bei jedem Refresh jeweils 128 Speicherzellen eines RAM-Bausteines gleichzeitig aufgefrischt werden, ergibt sich eine maximale Zeit von etwa 15,6 usec zwischen Refresh-Zyklen. Die in dieser Baugruppe eingesetzten RAMs Typ 4116 sind intern in einer 128 X 128 organisiert. Der Refresh-Zyklus wird unabhängig vom Zustand Mikroprozessors des Mikroprozessors ausgeführt. Eine spezielle "Arbiter-Schaltung" verhindert jedoch, daß gleichzeitig ein RAM-Zugriff und ein Refresh-Zyklus ausgeführt wird.