# LPL.RAM 16KB DY. CAAC08

#### Inhaltsverzeichnis

| Allgemeine Beschreibung der Baugruppe CAAC 08                               | 2  |

|-----------------------------------------------------------------------------|----|

| Die Kartenadresse                                                           | 2  |

| Die Schnittstelle der 16kB-Speicher- und Umschaltkarte                      | 3  |

| Die Schnittstelle zum alphaTronic-Systembus                                 | 3  |

| Die Schnittstelle zu den 48kB-RAM-Seiten                                    | 5  |

| Die Schnittstelle zu anderen Baugruppen                                     | 6  |

| übersichtsbild über die Speicherstruktur                                    | 7  |

| Die Seitenadressierung                                                      | 8  |

| Beispielprogramm für die Umschaltung zwischen den<br>Speicherseiten O und 1 | 9  |

| Die Logik zur Seitenauswahl                                                 | 10 |

| Die Erzeugung der Seitenselektionssignale PAGE O bis 3                      | 11 |

| Die Bildung der OEZ-Signale                                                 | 13 |

| Die Erzeugung der -5 Volt Betriebsspannung                                  | 14 |

| Die Stromaufnahme der 16kB-Speicher- und Umschaltkarte                      | 14 |

| Steckerbelegungsliste                                                       | 15 |

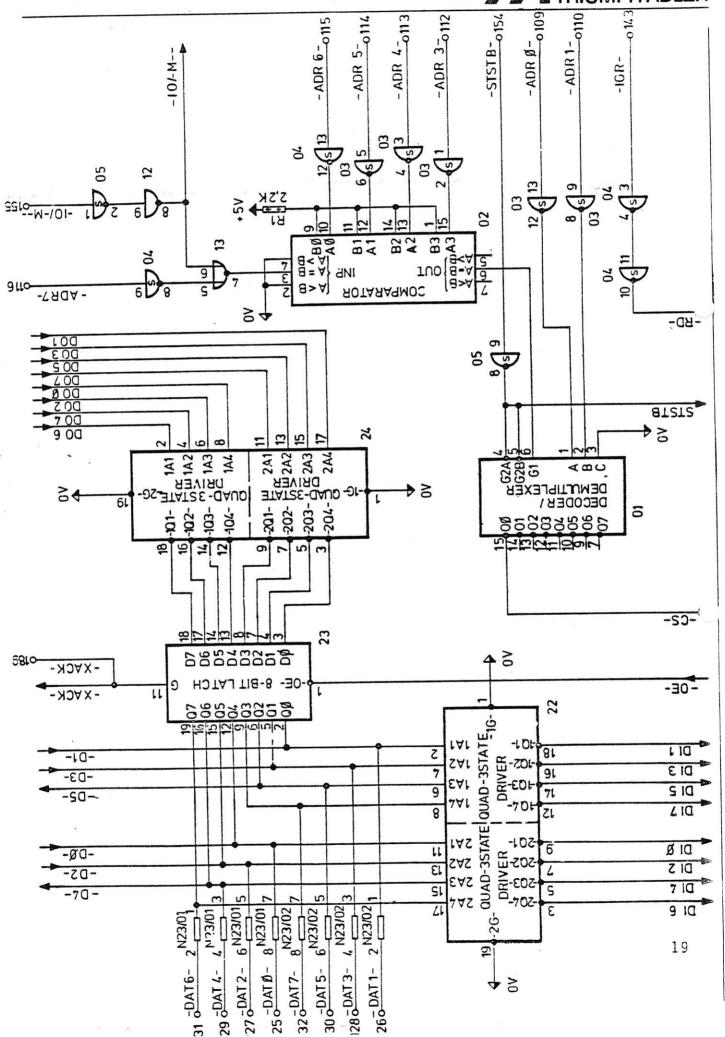

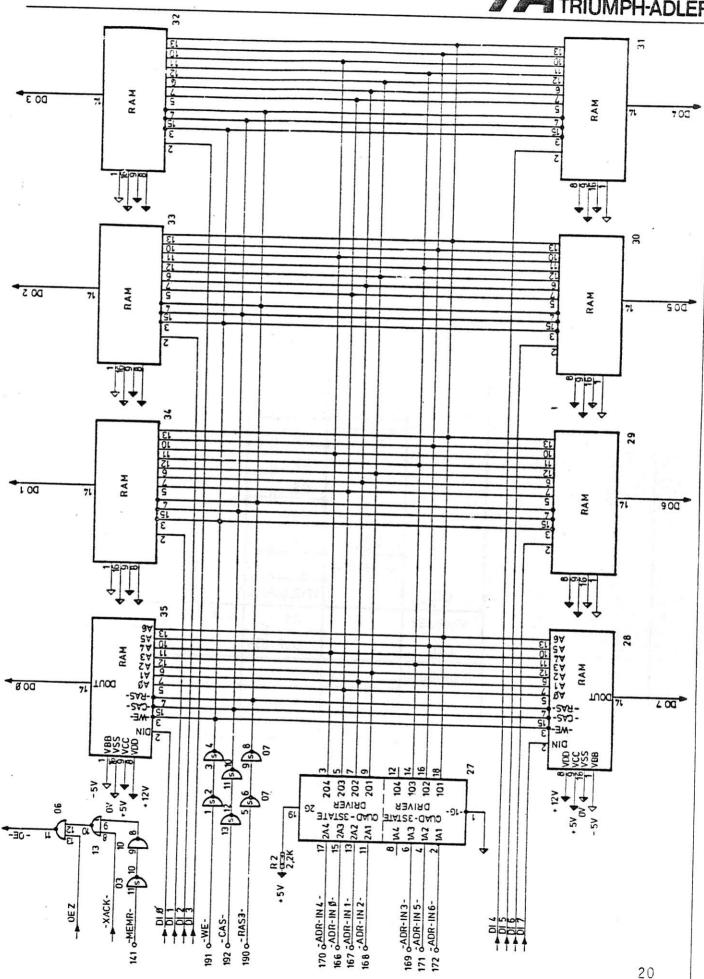

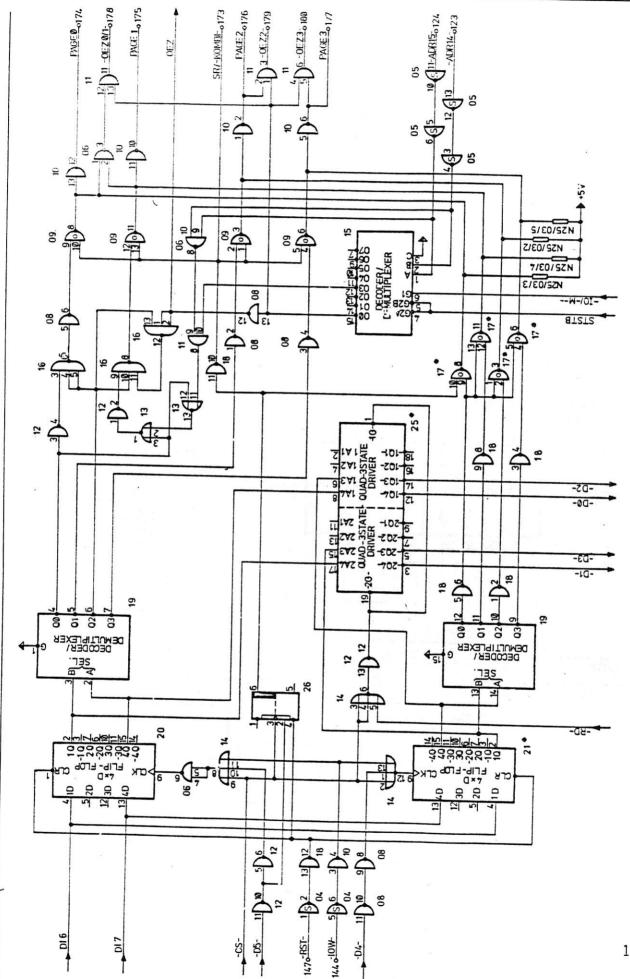

| Schaltbild                                                                  | 18 |

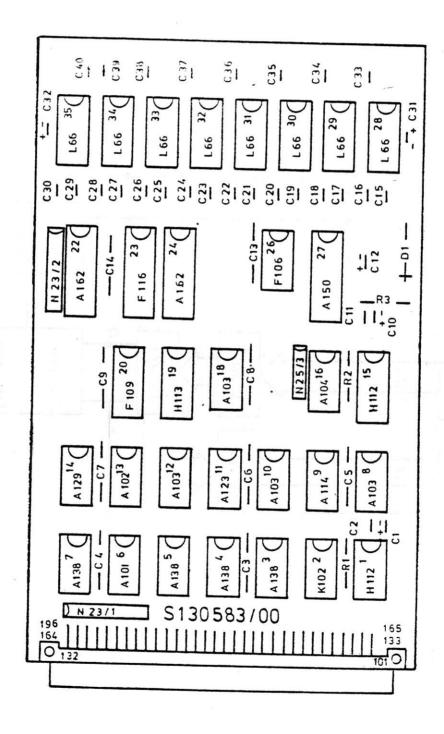

| Bestückungsplan                                                             | 22 |

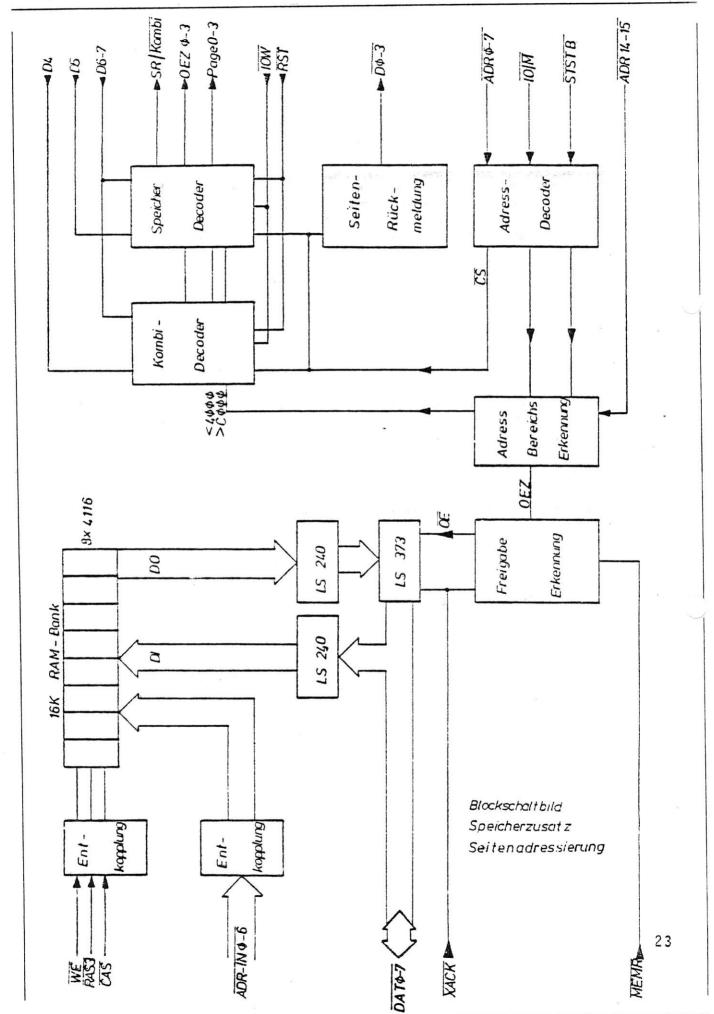

| Blockschaltbild der 16kB-Speicher- und Umschaltkarte                        | 23 |

Allgemeine Beschreibung der Baugruppe CAAC 08

Die Baugruppe CAAC 08 ist eine dynamische Speichereinheit mit einer Kapazität von 16kByte. Die eingesetzten RAM- Bausteine vom Typ 4116 haben eine maximale Zugriffszeit von 250 der RAM-Bausteine werden drei Versorgungsspannungen benötigt. Die Speicherorganisation der RAM-Bausteine beträgt 16k X 1 Bit.

Die Baugruppe verfügt über keinen eigenen Controller zur Steuerung der dynamischen RAMs. Diese Funktion übernimmt der 8202A RAM-Controller auf der 48kByte Baugruppe (CAAC 09).

Zusätzlich zu diesem 16kByte Speicherbereich befindet sich auf der Baugruppe die komplette Logik zur Seitenadressierung.

Die Baugruppe hat Einfach-Europakarten-Format und verfügt über eine 96polige Stiftleiste zur Verbindung mit dem alphaTronic-Systembus.

Ergänzend zu der nachfolgenden Beschreibung der Baugruppe CAAC 08 sind die Baugruppenbeschreibungen zu CAAC 05/06 und CAAC 09/10 zu beachten.

Die Kartenadresse

Die Baugruppe CAAC 08 belegt die hexadezimalen IO-Adressen 78 und 7C. Über diese Adressen erfolgt die Selektion der verschiedenen Speicherseiten.

Durch die nicht vollständige Ausdecodierung der IO-Adressen, bei der die Adreßleitung -ADR 2- nicht verwendet wird, ergibt sich die Primäradresse zu 78H und die Sekundäradresse zu 7CH.

Vereinbarungsgemäß wird zur Adressierung ausschließlich die Adresse 78H verwendet.

Die Schnittstelle der 16kB-Speicher- und Umschaltkarte

Die Verbindung der Speicher- und Umschaltkarte mit dem alphaTronic-Systembus erfolgt über die a- und b-Reihe (Pin 100 bis 164) der 96poligen VG-Leiste.

Die Verbindung der 16kB-Speicher- und Umschaltkarte zu der ersten 48kB-Speicherkarte (Seite 0/1), sowie zu den beiden, für spätere Erweiterungen vorgesehenen 48kB-Seiten 2 und 3, erfolgt über die c-Reihe der Steckerleiste.

Die Schnittstelle zum alphaTronic-Systembus

Alle Steuer- und Datenleitungen werden vom Systembus größtenteils durch invertierende Gatter mit Schmitt-Trigger-Eingängen entkoppelt.

Zur Begrenzung von Kurzschlußströmen, die beim Gegeneinanderschalten von Bustreibern kurzzeitig entstehen können, sind in jede Datenleitung zum Bus hin Widerstände von 150 Ohm eingefügt.

Die Datenleitungen -DAT O- bis -DAT 7- werden auf der Baugruppe nach ihrer Signalflußrichtung unterteilt. Der Hauptdatenstrom, dessen Signalflußrichtung auf die Baugruppe gerichtet ist, wird über IC 22 (74LS240), einen invertierenden Busleitungstreiber mit Schmitt-Trigger-Eingängen, entkoppelt. Die vom Bus herkommenden Datensignale -DAT- werden nach ihrer Invertierung mit DI bezeichnet.

Die Daten, welche beim Lesen aus dem 16kB-Speicher (Adreßbereich COOOH - FFFFH) anliegen, werden in einem 8-Bit-Latch (IC 23, 74LS373) zwischengespeichert. Mit diesem Latch ist keine Anpassung der H-aktiven Datensignale an den L-aktiven Systembus möglich. Aus diesem Grund ist IC 24 (74LS240), ein Inverter, den Eingängen des Latches vorgeschaltet.

Nach dem Wechsel des Signalpegels am Enable-Eingang G (IC 23, Pin 11) von High- auf Low-Pegel, werden die Daten an den Dateneingängen abgespeichert. Diese Daten bleiben solange gültig, wie Low-Pegel am G-Eingang anliegt. Der G-Eingang ist mit dem -XACK--Signal des 8202A RAM- Controllers auf der 48kB-RAM-Baugruppe (Seite 0/1) über Pin 189 der 96poligen VG-Leiste verbunden. Low-Pegel an -XACK- besagt, daß gültige Daten anliegen.

Die Freigabe der Latch-Ausgänge erfolgt über den -OE--Eingang an Pin 1. Während H-Pegel an diesem Eingang anliegt, sind die Ausgänge des Latches im hochohmigen Zustand (Tri-State).

Das Freigabesignal -OE- wird aus den Signalen -MEMR-,-XACKund OEZ nach der folgenden Boolschen Gleichung gebildet:

--MEMR- . -XACK- + OEZ- = -OE-

Im einzelnen haben die Signale folgende Bedeutung:

-MEMR- Low-Pegel zeigt an, daß eine Speicheradresse angesprochen ist.

-XACK- Low-Pegel zeigt an, daß Daten gültig sind.

OEZ Dieses Signal hat High-Pegel, wenn eine Speicheradresse im Bereich von COOOH bis FFFFH angesprochen ist.

Hieraus ergibt sich für das -OE--Signal, daß dieses immer dann Low-Pegel hat, wenn aus dem Speicheradreßbereich von COOOH bis FFFFH gelesen wird, und die Daten auf den Datenleitungen gültig anstehen.

Die Schnittstelle zu den 48kB-RAM-Seiten

Die Schnittstellensignale zu den 48kB-RAM-Seiten lassen sich in zwei Gruppen unterteilen.

Gruppe 1: Signale zwischen der ersten 48kB-RAM-Speicherseite und der 16kB-Speicher- und Umschaltkarte.

Die erste Gruppe wird gebildet aus den Schnittstellensignalen zur ersten 48kB-RAM-Seite (Seite 0/1). Hierzu zählen die im folgenden beschriebenen Signale:

-ADR-IN O- bis -ADR-IN 6-

Signalleitungen für die gemultiplexten Row- und Column-Adressen des 8202A RAM-Controllers auf der ersten 48kB-RAM-Seite. Diese Signale werden auf der Baugruppe CAAC 08 durch einen nichtinvertierenden Leitungstreiber (IC 27, 74LS241) entkoppelt.

-WE-

Low-Pegel auf dieser Signalleitung schaltet die RAMs in den Schreib-Mode. Die Datenausgänge (DOUT, Pin 14) der RAMs befinden sich während dieser Zeit im hochohmigen Zustand.

-WE- ist ein Ausgangssignal des 8202A RAM-Controllers.

-RAS 3-

Mit der 1/0-Flanke des -RAS 3--Signals wird die vom RAM-Controller über die Adreßausgänge ausgegebene Reihenadresse den RAM-Bausteinen übergeben. Das Signal -RAS 3- nimmt nur dann Low-Pegel an, wenn eine Speicheradresse im Bereich von hexadezimal COOO bis FFFF angesprochen ist. Low-Pegel auf diesem Signal ist zusätzlich noch bei einem Refresh-Zyklus möglich, wobei die Signale -RAS 0- bis -RAS 2- ebenfalls Low-Pegel haben.

-CAS-

Mit der 1/0-Flanke dieses Signals wird die Spaltenadresse des RAM-Controllers übergeben. Das Signal -CAS- nimmt jedesmal dann Low-Pegel an, wenn der RAM-Controller eine Spaltenadresse ausgibt.

Die Signale -WE-, -RAS 3- und -CAS- werden auf der Baugruppe durch jeweils zwei invertierende Gatter mit Schmitt-Trigger-Eingängen entkoppelt (IC 07).

-0EZ 0/1-

Freigabesignal für den Datenausgangsbuffer auf der ersten 48kB-RAM-Speicherseite.

Gruppe 2: Steuersignale zu weiteren Speicherseiten

Zur dieser Gruppe gehören die Signale, welche die Freigabe der zusätzlichen, für spätere Erweiterungen vorgesehenen 48kB-RAM-Seiten steuern. Diese Signale werden mit PAGE 2 und PAGE 3 sowie -OEZ 2- und -OEZ 3- bezeichnet.

Die Schnittstelle zu anderen Baugruppen

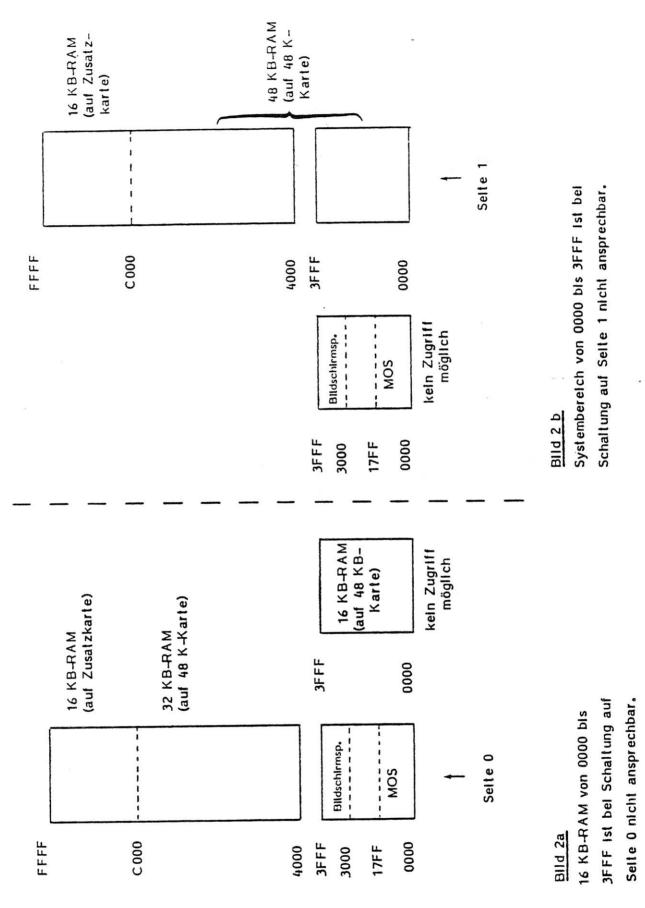

Diese Schnittstellensignale sind PAGE O und SR/-KOMBI-. Das Signal SR/-KOMBI- wird in der alphaTronic nicht verwendet und muß immer auf High-Pegel liegen. Wenn auf der Seite O gearbeitet wird, hat das Signal PAGE O High-Pegel. Unter Seite O verstehen wir den MOS- und RAM-Adreßbereich auf der CPU-Baugruppe, den Bildwiederholspeicherbereich auf der BC-10-Baugruppe sowie den freien Anwenderspeicherbereich von 4000H bis FFFFH. Wird nicht mit dieser Seite O gearbeitet, so muß der Adreßbereich von O bis 3FFFH der Seite O gesperrt werden. Hierzu sind die Adreßbereichsfreigabesignale auf den Baugruppen CPU und BC-10 mit dem Signal PAGE O verknüpft.

Siehe hierzu auch das Bild auf der folgenden Seite.

## Die Seitenadressierung

Die Logik zur Seitenadressierung verwaltet die Adreßerkennung der 16k-Bank und bis zu drei 48kB-Speicherkarten.

> Seite O: Erkennung der 16kB-Bank ab COOOH und der oberen 32kB der 48kB-Karte 1 ab der hexadezimalen Adresse 4000. Im Bereich von 0 bis 3FFFH liegt der MOS und Bildwiederholspeicherbereich.

Seite 1: Erkennung der 16kB-Bank ab COOOH und der gesammten 48kB-Karte 1 ab der Adresse 0 bis BFFFH.

Seite 2: Erkennung der 16kB-Bank ab COOOH und der gesammten 48kB-Karte 2 ab der Adresse 0 bis BFFFH.

Seite 3: Erkennung der 16kB-Bank ab COOOH und der gesammten 48kB-Karte 3 ab der Adresse 0 bis BFFFH.

Die Umschaltung der Speicherseiten erfolgt über die IO-Adresse 78H. Hierzu muß durch einen Schreibbefehl auf diese Adresse ein bestimmtes Datum ausgegeben werden.

Die nachfolgende Tabelle zeigt die Bedeutung der Datenbits bei der Speicherseitenauswahl.

| b7 , | b6 | b5 | b4 - b0 | Seite | entspr. HexWert |

|------|----|----|---------|-------|-----------------|

| 0    | 0  | 1  | 0       | 0     | 20              |

| 0    | 1  | 1  | 0       | 1     | 60              |

| 1    | 0  | 1  | 0       | 2 -   | AO              |

| 1    | 1  | 1  | 0       | 3     | EO              |

Beispielprogramm für die Umschaltung zwischen den Speicherseiten  $\mathbf{0}$  und  $\mathbf{1}$

Im Computersystem alphaTronic wird die Umschaltung zwischen den beiden Seiten O und 1 bei Verwendung von 64kB-CP/M voll unterstützt. Der Anwender braucht somit die Auswahl der benötigten Speicherseite nicht selbst zu treffen.

Um einen kleinen Einblick in die Vorgehensweise bei der Umschaltung zwischen den Speicherseiten O und 1 zu erhalten, sind die folgenden Programmteile gedacht.

| ;<br>; | KANAL<br>LXI                     | EQU 78H<br>SP,OFFFFH         | ;IO-Adr. für Seitenumsch.<br>;Stachpointer nach oben                                     |

|--------|----------------------------------|------------------------------|------------------------------------------------------------------------------------------|

| ;      | CALL                             | C01                          | ;MOS-Routine Console-Outp.                                                               |

|        | •                                | •                            | •                                                                                        |

| ;      |                                  |                              |                                                                                          |

| ;      | Subroutin                        | es                           |                                                                                          |

| co1:   | CALL<br>CALL<br>CALL<br>RET      | SEIO<br>CO<br>SEI1           | ;Auf MOS-Seite umschalten<br>;CO-Routine aufrufen<br>;Auf 64k-RAM-Seite zurück           |

| ;      |                                  |                              |                                                                                          |

| ŚEIO:  | PUSH<br>MVI<br>OUT<br>POP<br>RET | PSW<br>A,20H<br>KANAL<br>PSW | ;Akku retten wegen OUT<br>;Byte für Seite O<br>;Byte über IO 78 ausgeben<br>;Akku zurück |

| ;      |                                  |                              | 0.17                                                                                     |

| SEI1:  | PUSH<br>MVI<br>OUT<br>POP<br>RET | PSW<br>A,60H<br>KANAL<br>PSW | ;Akku retten wegen OUT<br>;Byte für Seite 1<br>;Byte über IO 78 ausgeben<br>;Akku zurück |

Die Logik zur Seitenauswahl

Zur Auswahl der verschiedenen Speicherseiten muß über die IO-Adresse 78H, wie im Kapitel "Die Seitenadressierung" in Tabellenform angegeben, ein bestimmtes Datum ausgegeben werden.

Bit 6 und 7 dieses Datenwortes werden in einem D-Flipflop (IC 20, 74LS175) abgespeichert. Als Übernahmeimpuls muß am CLK-Eingang (IC 20, Pin 9) eine O/1-Flanke erscheinen. Dieses Übernahmesignal entsteht mit der O/1-Flanke des -IOW-- Signals, bei gleichzeitigem anliegen der IO-Adresse 78H und bei gesetztem Datenbit b5. Bei gesetztem Datenbit b5 liegt die -DAT5--Leitung auf Low-Pegel.

Die auf diese Art zwischengespeicherte Dateninformation der Datenleitungen DI6 und DI7 wird auf die Dateneingänge A und B eines Binärdekoder/ Demultiplexer ICs (IC 19, Pin 2 und 3, 74LS139) gegeben. Der Freigabeeingang G (Pin 1) ist fest mit Low-Pegel verbunden.

Abhängig von der Eingangsinformation an den Eingängen A und B liegt an einem Ausgang (QO bis Q3) Low-Pegel an.

Die Abhängigkeit der Ausgänge von der Eingangsinformation an A und B zeigt die folgende Tabelle.

| Signal<br>Ein/Ausg.<br>Pin | DI6<br>B<br>3 | DI7<br>A<br>2 | -SEITE 0-<br>QO<br>4 | -SEITE 2-<br>Q1<br>5 | -SEITE 1-<br>Q2<br>6 | -SEITE 3 |

|----------------------------|---------------|---------------|----------------------|----------------------|----------------------|----------|

|                            | L             | L             | L                    | Н                    | Н                    | Н        |

|                            | L             | Н             | Н                    | L                    | Н                    | Н        |

|                            | Н             | L             | Н                    | Н                    | L,                   | Н        |

| -                          | Н             | Н             | Н                    | Н                    | Н                    | L        |

Die Auswahl, ob die angesprochene Adresse der jeweils ausgewählten Seite auf der entsprechenden 48kB-Speicherkarte oder auf der 16kB-Zusatzkarte liegt, wird durch die den Demultiplexern nachgeschaltete Lokik getroffen.

Die Erzeugung der Seitenselektionssignale PAGE 0 bis PAGE 3

Die Selektionssignale, für die im Endausbau vorgesehenen maximal drei möglichen 48kB-Speicherkarten, werden auf dieser Baugruppe erzeugt. Diese Signale tragen die Bezeichnung PAGE 0 bis PAGE 3.

Die PAGE-Signale lassen sich durch zwei verschiedene Logikteile auf dieser Baugruppe erzeugen. Die jeweils zusammengehörigen Ausgänge dieser Logikteile sind über "Wired-Or"-Verbindungen verknüpft. Diese "Wired-Or"-Logik wird gebildet aus den ICs 09 und 17, deren "Open-Collector"-Ausgänge über 2,2 k0hm "Pull-up"-Widerstände mit +5 Volt-Potential verbunden sind.

Zur Erzeugung eines High-aktiven PAGE-Signals ist dieser "Wired-Or"-Verknüpfung ein invertierendes Gatter nachgeschaltet.

Die Umschaltung zwischen den beiden durch die zwei Logikteile erzeugten PAGE-Signale erfolgt über einen Eingang eines jeden NAND-Gatters von IC 09 und 17. Diese Eingänge werden über den -Q--Ausgang des Flipflops (IC 26, Pin 6) angesteuert. Dieser Ausgang muß bei Einsatz dieser Baugruppe in der alphaTronic immer Low-Pegel haben. Somit liegt an dem zur Steuerung verwendeten Eingang eines jeden NAND-Gatters von IC 09 H-Pegel an. Durch diese Beschaltung liegt am Ausgang eines jeden Gatters von IC 09 das invertierte Signal des anderen Eingangs an.

Dieser zweite Logikteil, gebildet aus IC 21, dem zweiten Demultiplexer aus IC 19, sowie IC 17 wird bei Einsatz dieser Baugruppe im Computersystem alphaTronic nicht benötigt.

#### PAGE 0

Das Signal des QO-Ausgangs (IC 19, Pin 4) wird invertiert und zusammen mit dem Q2-Ausgangssignal in einem NAND-Gatter verknüpft. Der Ausgang dieser NAND-Verknüpfung (IC 16, Pin 6) hat somit Low-Pegel wenn Seite O angesprochen ist.

An Pin 10 von IC 09 muß immer High-Pegel anliegen, so daß der Ausgang an Pin 8 immer Low-Pegel besitzt, wenn Seite 0 selektiert ist. Zur Bildung des High-aktiven Seitenselektionssignals PAGE 0 an Pin 174 der Steckerleiste, ist ein weiterer Inverter (IC 10, Pin 12 und 13) erforderlich.

#### PAGE 1

Das Signal PAGE 1 wird gebildet aus den Ausgangssignalen Q0 und Q2 des Demultiplexers (IC 19, Pin 4 und 6). Zusätzlich werden diese Signale noch mit Adreßbereichssignalen verknüpft, die mit dem Decoder/ Demultiplexer (IC 15, 74LS138) gewonnen werden.

Das Ausgangssignal an Pin 8 von IC 16 hat dann H-Pegel, wenn Seite O angesprochen wird und die Adresse im Bereich von 4000H bis FFFFH liegt oder aber wenn Seite 1 ausgewählt ist. Dieses Ausgangssignal entspricht dem Signal PAGE 1 an Pin 175 der Steckerleiste.

#### PAGE 2 und PAGE 3

H-Pegel auf den Signalleitungen PAGE 2 und PAGE 3 selektiert die zweite oder dritte zusätzliche 48kB-Speicherkarte im System. Diese Selektionssignale werden aus den Low-aktiven Ausgängen des Demultiplexers (IC 19, Pin 5 und 7) gewonnen.

Die Signale PAGE 2 und PAGE 3 sind für spätere Systemerweiterungen vorgesehen. Die Bildung der OEZ-Signale

Die Signale -OEZ O bis OEZ 3- werden zusammen mit weiteren Steuersignalen zu einem Freigabesignal für die Datenausgangsbuffer auf den verschiedenen 48kB-Speicherseiten verknüpft.

OEZ

Das Signal OEZ wird zusammen mit weiteren Signalen zu dem Freigabesignal -OE- verknüpft. Das Signal OEZ hat immer High-Pegel, wenn der Speicheradreßbereich von COOOH bis FFFFH angesprochen ist.

-OEZ 0/1-

Das Signal -OEZ O/1- an Pin 178 hat Low-Pegel, wenn Seite O oder Seite 1 selektiert ist und die Adresse im Bereich von OOOOH bis BFFFH liegt.

-OEZ 2-

Dieses Signal an Pin 179 hat Low-Pegel, wenn die Seite 2 angesprochen wird (H-Pegel an PAGE 2) und die Adresse im Bereich von 0000H bis BFFFH liegt.

-OEZ 3-

Dieses Signal an Pin 180 hat Low-Pegel, wenn die Seite 3 angesprochen wird (H-Pegel an PAGE 3) und die Adresse im Bereich von 0000H bis BFFFH liegt.

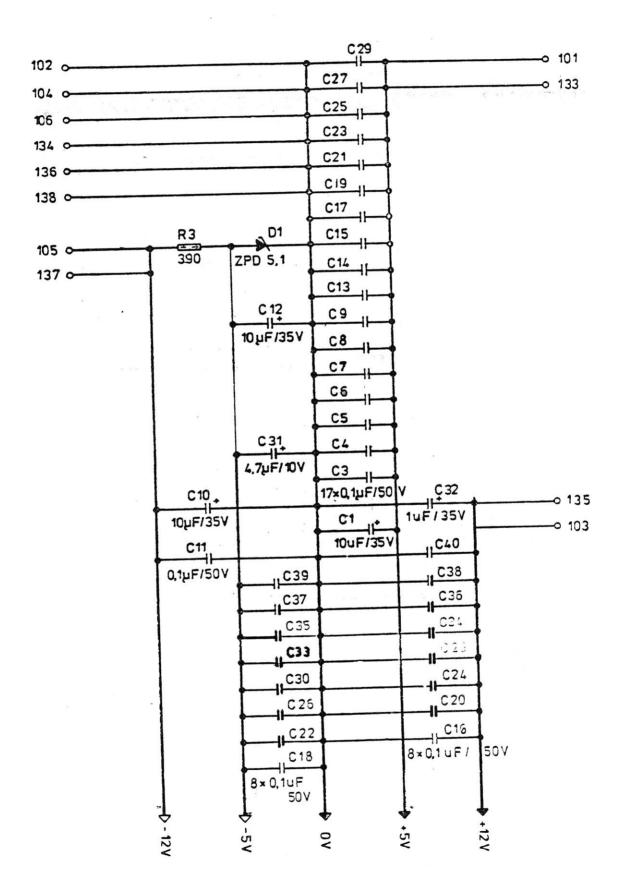

Die Erzeugung der -5 Volt Betriebsspannung

Die hier verwendeten dynamischen RAM-Bausteine vom Typ 4116 benötigen außer +5 und +12 Volt auch eine negative Betriebsspannung von -5 Volt. Diese Spannung wird auf der Baugruppe aus der -12 Volt Spannung gewonnen. Die Schaltung zur Gewinnung der -5 Volt Betriebsspannung besteht aus dem Strombegrenzungswiderstand (R 3, 390 Ohm), der den Arbeitspunkt auf (D1, ZPD 5,1). Diese Diode hat eine Durchbruchspannung von (D1, ZPD 5,1). Diese Diode hat eine Durchbruchspannung von gewonnenen negativen Betriebsspannung von -5 Volt +/-5% wird der Kondensator C12 benötigt.

Die Stromaufnahme der 16kB-Speicher- und Umschaltkarte

| + 5 V | +/- | 5% | Stromaufnahme: | typ:<br>max: | 280<br>340 | m A<br>m A |

|-------|-----|----|----------------|--------------|------------|------------|

| +12 V | +/- | 5% | Stromaufnahme: | typ:<br>max: |            |            |

| -12 V | +/- | 5% | Stromaufnahme: |              | 20         |            |

## Steckerbelegungsliste:

| PIN                                                                       | Bezeichnung                                            | Erklärung                                                                                                                           |

|---------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 101<br>102<br>103<br>104<br>105<br>106<br>107                             | + 5 V<br>0 V<br>+12 V<br>0 V<br>-12 V<br>0 V           |                                                                                                                                     |

| 108<br>109<br>110                                                         | -ADR 0-<br>-ADR 1-                                     | Adreßbit 0<br>Adreßbit 1                                                                                                            |

| 111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>120<br>121 | -ADR 3-<br>-ADR 4-<br>-ADR 5-<br>-ADR 6-<br>-ADR 7-    | Adreßbit 3<br>Adreßbit 4<br>Adreßbit 5<br>Adreßbit 6<br>Adreßbit 7                                                                  |

| 122<br>123<br>124<br>125<br>126<br>127<br>128<br>129<br>130<br>131        | -ADR 14ADR 15DAT 0DAT 1DAT 2DAT 3DAT 4DAT 5DAT 6DAT 7- | Adreßbit 14 Adreßbit 15 Daten-Bit 0 Daten-Bit 1 Daten-Bit 2 Daten-Bit 3 Daten-Bit 4 Daten-Bit 5 Daten-Bit 5 Daten-Bit 6 Daten-Bit 7 |

## Steckerbelegungsliste

| PIN                                           | Bezeichn                                     | ung | Erläu            | ıterunge    | n       |

|-----------------------------------------------|----------------------------------------------|-----|------------------|-------------|---------|

| 133<br>134<br>135<br>136<br>137<br>138<br>139 | + 5 V<br>0 V<br>+12 V<br>0 V<br>-12 V<br>0 V |     |                  |             |         |

| 140<br>141<br>142                             | -MEMR-                                       |     | Memor            | y-Read      |         |

| 143<br>144<br>145                             | - I OR -<br>- I OW-                          |     | I/O-Re<br>I/O-Wi | ead<br>rite |         |

| 146<br>147<br>148<br>149                      | -RST-                                        |     | Reset            | intern      |         |

| 150<br>151<br>152<br>153                      |                                              |     |                  |             |         |

| 154                                           | -STSTB-<br>-IO/-M                            |     | Status<br>IO-Erk | Strobe      | (-ALE-) |

| 157<br>158<br>159<br>160<br>161               |                                              |     |                  |             |         |

| 162<br>163<br>164                             |                                              |     |                  |             |         |

### Steckerbelegungsliste

| PIN                                                                                                                                      | Bezeichnung                                                                                                | Erläuterungen                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 165<br>166<br>167<br>168<br>169<br>170<br>171<br>172<br>173<br>174<br>175<br>176<br>177<br>178<br>179<br>180<br>181<br>182<br>183<br>184 | -ADR-IN 0ADR-IN 1ADR-IN 2ADR-IN 3ADR-IN 5ADR-IN 6- SR/-Kombi- PAGE 0 PAGE 1 PAGE 2 PAGE 3 -OEZO/1OEZ2OEZ3- | Adreßbit 0 Adreßbit 1 Adreßbit 2 Adreßbit 3 Adreßbit 4 Adreßbit 5 Adreßbit 6 Speicher/ Interface Seite 0 Seite 1 Seite 2 Seite 3 Freigabe Zusatzkarte 1 Freigabe Zusatzkarte 2 Freigabe Zusatzkarte 3 |

| 185<br>186<br>187<br>188<br>189<br>190<br>191<br>192<br>193<br>194<br>195                                                                | - X A C K -<br>- R A S 3 -<br>- W E -<br>- C A S -                                                         | Transfer Acknoledge<br>Row Adress Strobe<br>Write Enable<br>Column Adres Strobe                                                                                                                       |

. IN BAUGRUPPE CAACOB NICHT BESTÜCKT